Back باور 6 Arabic POWER6 French POWER6 Hungarian POWER6 Italian POWER6 Japanese POWER6 Dutch POWER6 NB POWER6 Russian POWER6 Chinese

This article's use of external links may not follow Wikipedia's policies or guidelines. (September 2017) |

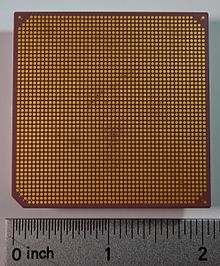

Power6 CPU | |

| General information | |

|---|---|

| Launched | 2007 |

| Designed by | IBM |

| Performance | |

| Max. CPU clock rate | 3.6 GHz to 5.0 GHz |

| Cache | |

| L1 cache | 64+64 KB/core |

| L2 cache | 4 MB/core |

| L3 cache | 32 MB/chip (off-chip) |

| Architecture and classification | |

| Technology node | 65 nm |

| Instruction set | Power ISA (Power ISA v.2.05) |

| Physical specifications | |

| Cores |

|

| History | |

| Predecessor | POWER5 |

| Successor | POWER7 |

| POWER, PowerPC, and Power ISA architectures |

|---|

| NXP (formerly Freescale and Motorola) |

| IBM |

|

| IBM/Nintendo |

| Other |

| Related links |

| Cancelled in gray, historic in italic |

The POWER6 is a microprocessor developed by IBM that implemented the Power ISA v.2.05. When it became available in systems in 2007, it succeeded the POWER5+ as IBM's flagship Power microprocessor. It is claimed to be part of the eCLipz project, said to have a goal of converging IBM's server hardware where practical (hence "ipz" in the acronym: iSeries, pSeries, and zSeries).[1]

- ^ "A Mainframe Roadmap". Isham Research. Archived from the original on 2016-03-03.